## **Data Parallel C++**

Mastering DPC++ for Programming of Heterogeneous Systems using C++ and SYCL

## Chapters 1-4 UNEDITED ADVANCE REVIEW COPY

Ben Ashbaugh, James Brodman, Michael Kinsner, John Pennycook, Xinmin Tian, and James R. Reinders

Apress

### Data Parallel C++: Mastering DPC++ for Programming of Heterogeneous Systems using C++ and SYCL

#### Copyright © 2020 by Intel Corporation

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

ISBN-13 (pbk): TBA

ISBN-13 (electronic): TBA

Trademarked names, logos, and images may appear in this book. Rather than use a trademark symbol with every occurrence of a trademarked name, logo, or image we use the names, logos, and images only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Intel, the Intel logo, Intel Optane, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

Khronos and the Khronos Group logo are trademarks of the Khronos Group Inc. in the U.S. and/or other countries.

OpenCL and the OpenCL logo are trademarks of Apple Inc. in the U.S. and/or other countries.

OpenMP and the OpenMP logo are trademarks of the OpenMP Architecture Review Board in the U.S. and/or other countries.

SYCL and the SYCL logo are trademarks of the Khronos Group Inc. in the U.S. and/or other countries.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit www.intel.com/benchmarks.

Performance results are based on testing as of dates shown in configuration and may not reflect all publicly available security updates. See configuration disclosure for details. No product or component can be absolutely secure.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at www.intel.com.

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. Notice revision #20110804.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Managing Director, Apress Media LLC: Welmoed Spahr Acquisitions Editor: Natalie Pao Development Editor: James Markham Coordinating Editor: Jessica Vakili

Distributed to the book trade worldwide by Springer Science+Business Media New York, 1 New York Plaza, New York, NY 10004. Phone 1-800-SPRINGER, fax (201) 348-4505, e-mail <u>orders-ny@springer-sbm.com</u>, or visit <u>www.springeronline.com</u>. Apress Media, LLC is a California LLC and the sole member (owner) is Springer Science + Business Media Finance Inc (SSBM Finance Inc). SSBM Finance Inc is a **Delaware** corporation.

For information on translations, please e-mail rights@apress.com, or visit http://www.apress.com/rights-permissions.

Apress titles may be purchased in bulk for academic, corporate, or promotional use. eBook versions and licenses are also available for most titles. For more information, reference our Print and eBook Bulk Sales web page at <a href="http://www.apress.com/bulk-sales">http://www.apress.com/bulk-sales</a>.

Any source code or other supplementary material referenced by the author in this book is available to readers on GitHub via the book's product page, located at TBA. For more detailed information, please visit <u>http://www.apress.com/source-code</u>

| Chapter 1 - Introduction1                           |

|-----------------------------------------------------|

| What is Data-Parallel Programming?2                 |

| What are Heterogeneous Systems?3                    |

| Enjoy the Journey – This is something BIG4          |

| Parallel Programming in C++4                        |

| Journey to Parallelism, Scaling, Portability4       |

| First look at DPC++ code6                           |

| Why DPC++?6                                         |

| Why must it be a first-class citizen?8              |

| Made for each other: Data parallelism and Big Data8 |

| SYCL, DPC++, C++9                                   |

| Khronos SYCL9                                       |

| DPC++9                                              |

| C++10                                               |

| Why Heterogeneous Systems?11                        |

| Platform Model13                                    |

| Multiarchitecture (aka "Fat") Binaries14            |

| Compilation Model14                                 |

| Truth and Fallacy of Write Once, Run Everywhere15   |

| Direct programming17                                |

| Why Data Parallelism?18                             |

| Think (Data) Parallel18                             |

| Intranode, not multinode, parallelism19             |

| Other Accelerator Programming Models19              |

| Evolution of SYCL (thus far)22                      |

### **TABLE OF CONTENTS**

| March 2015 – SYCL 1.2     | 22 |

|---------------------------|----|

| April 2019 – SYCL 1.2.1r5 | 23 |

| SYCL 1.2.1r6 and beyond   | 23 |

| SYCL Provisional 2.2      | 23 |

| Chapter 2 – Where Code Executes                               | 25 |

|---------------------------------------------------------------|----|

| Single source                                                 | 25 |

| Host code                                                     | 26 |

| Device code                                                   | 27 |

| Choosing a device on which to execute                         | 28 |

| Method#1: Just run on a device (don't care what type)         | 28 |

| Queues                                                        | 29 |

| Binding a queue to a device, when any device will do          | 31 |

| Method#2: Using the host device for development and debugging | 32 |

| Method#3: Using a GPU (or other accelerator)                  | 34 |

| Device types<br>Accelerator devices                           |    |

| When device selection fails                        |    |

|----------------------------------------------------|----|

| Method#4: Using multiple devices                   |    |

| Method#5: Custom (very specific) device selection  | 40 |

| Writing a custom selector                          | 40 |

| device_selector base class                         | 40 |

| Mechanisms to score a device                       | 41 |

| Three paths to device code execution on CPU        | 42 |

| Language constructs that generate work on a device | 43 |

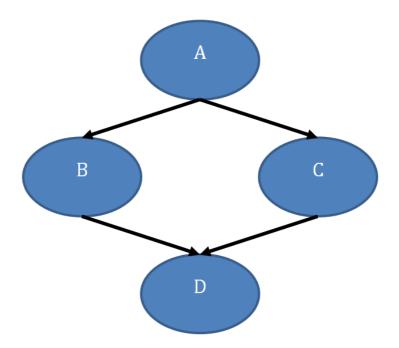

| Introduction to the SYCL Graph                     | 43 |

| Where is the device code?                          | 44 |

|                                                    |    |

#### **Table of Contents**

| Device dispatch and memory copy mechanisms | 45 |

|--------------------------------------------|----|

| Fallback                                   | 48 |

| Chapter 3 – Data Management                                    | 51 |

|----------------------------------------------------------------|----|

| The Data Management Problem                                    | 52 |

| Device Local vs. Device Remote                                 | 52 |

| Managing Multiple Memories                                     | 53 |

| Explicit data movement                                         | 53 |

| Implicit data movement                                         | 54 |

| Selecting the right strategy: explicit or implicit             | 54 |

| USM, Buffers, and Images                                       | 55 |

| Unified Shared Memory                                          | 55 |

| Accessing memory through pointers                              | 55 |

| USM and Data Movement                                          | 56 |

| Explicit Data Movement in USM<br>Implicit Data Movement in USM |    |

|                                                                |    |

| Buffers                                                        |    |

| Creating buffers                                               | 59 |

| Accessing buffers                                              | 60 |

| Access Modes                                                   | 61 |

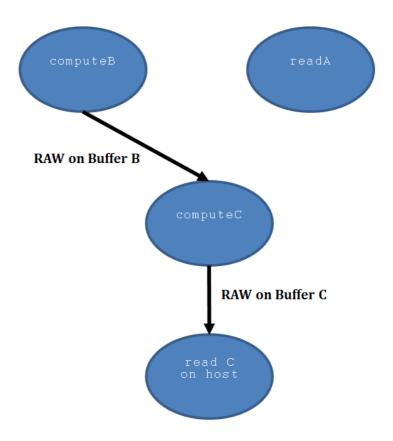

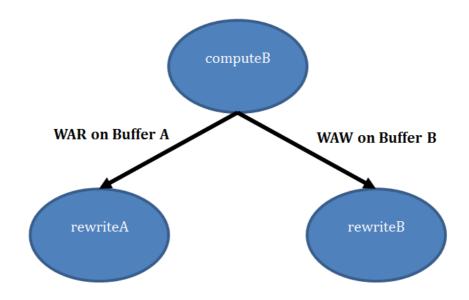

| Ordering the Uses of Data                                      | 62 |

| In-order Queues                                                | 64 |

| Out-of-Order (OoO) Queues                                      | 65 |

| Explicit Dependences with Events                               | 65 |

| Implicit Dependences with Accessors                            | 67 |

| Choosing a Data Management Strategy                            |    |

### TABLE OF CONTENTS

| Chapter 4 – Expressing Parallelism                                                                                                              | 75       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

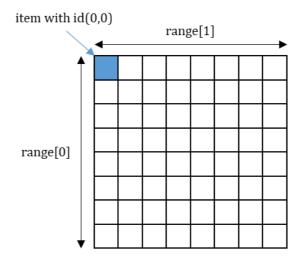

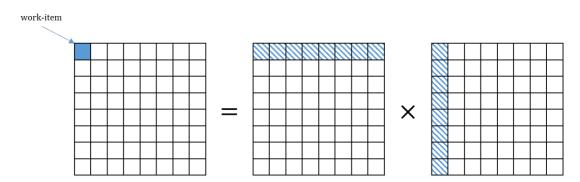

| Parallelism within Kernels                                                                                                                      | 75       |

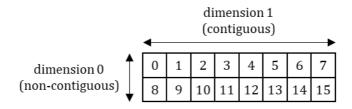

| Multi-dimensional Kernels                                                                                                                       | 76       |

| Loops vs. Kernels                                                                                                                               | 77       |

| Overview of Language Features                                                                                                                   | 79       |

| Separating Kernels from Host Code                                                                                                               | 79       |

| Different Forms of Parallel Kernel                                                                                                              | 79       |

| Basic Data Parallel Kernels                                                                                                                     | 80       |

| Basic Data Parallel Kernels: Execution Model                                                                                                    | 80       |

| Basic Data Parallel Kernels: Syntax                                                                                                             | 81       |

| Basic Data Parallel Kernels: Important Classes<br>The range Class<br>The id Class<br>The item Class                                             | 83<br>84 |

| Explicit ND-Range Kernels                                                                                                                       | 86       |

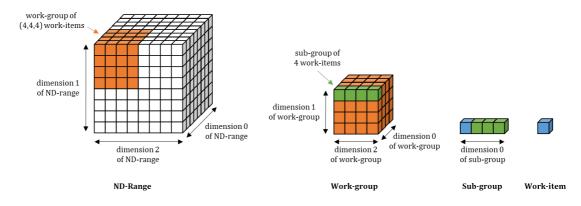

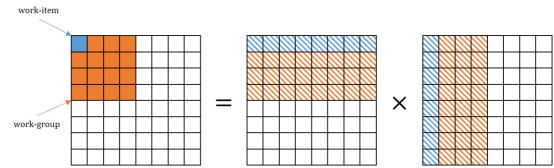

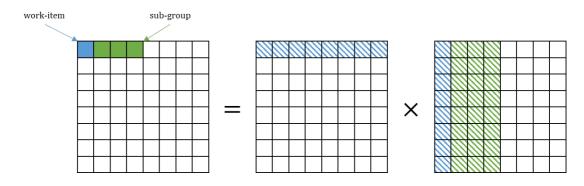

| Explicit ND-Range Parallel Kernels: Execution Model<br>Work-items<br>Work-groups<br>Sub-groups                                                  | 88<br>88 |

| Explicit ND-Range Data Parallel Kernels: Syntax                                                                                                 | 91       |

| Explicit ND-Range Data Parallel Kernels: Important Classes<br>The nd_range Class<br>The nd_item Class<br>The group Class<br>The sub_group Class |          |

| Hierarchical Parallel Kernels                                                                                                                   |          |

| Hierarchical Data Parallel Kernels: Execution Model                                                                                             | 108      |

| Hierarchical Data Parallel Kernels: Syntax                                                                                                      | 108      |

|                                                                                                                                                 |          |

#### **Table of Contents**

| The h_item Class                          |     |

|-------------------------------------------|-----|

| The private_memory Class                  | 113 |

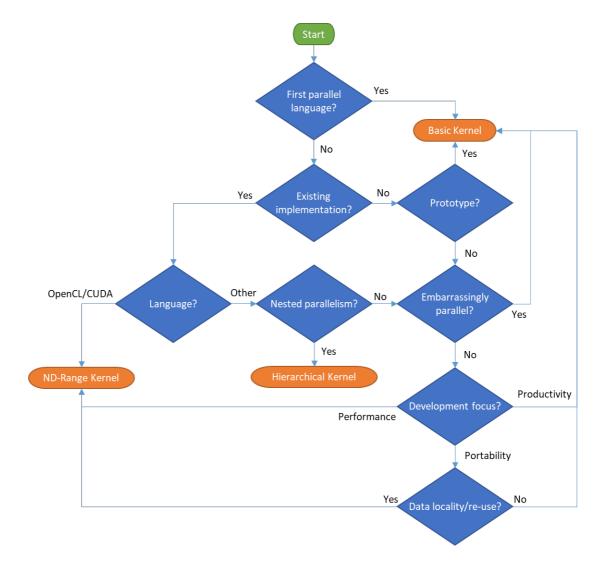

| Choosing a Kernel Form                    | 114 |

| Summary                                   | 116 |

| For More Information                      |     |

| How to provide Feedback, Download Samples | 118 |

### **TABLE OF CONTENTS**

#### FOR THIS BOOK PREVIEW (CHAPTERS 1-4): ERRATA, NOTES, DOWNLOADS, FEEDBACK, ETC.

Please check our "preview book" website for information including errata, updates, and downloads (includes all sample code): https://tinyurl.com/book-dpcpp

We will also list some additional resources as they become available.

Your feedback is welcome. You can email James Reinders at dpc++@jamesreinders.com with any suggestions, encouragement, criticism, or questions that you may have. James will be sure to share any feedback that you send with all the authors.

Of course – watch for the full book, by mid-2020, available from Apress (no charge for PDF for the completed book, print copies will be available too).

https://tinyurl.com/book-dpcpp

#### **Preface for Chapter 1-4 Preview**

We are pleased to share a preview of the beginning of our new book on data parallel programming in C++, for Heterogeneous Systems, using DPC++.

We have worked hard to make this text very useful — we believe it has been wellreviewed for content and correctness. However, we are far from done on formatting at this point, so we ask you to look past the imperfect layout and formatting in this preview edition.

While we will finish this book by mid-2020, we have decided to release the first four chapters to introduce DPC++ now. This will afford you, the reader, a chance to give DPC++ a try, to learn, and to give us feedback.

These four chapters form an excellent introduction to the entire topic. Remaining chapters will dive deeper into specific topics (we've attached a list at the end of this posting).

All the features of DPC++, and SYCL, are supported by both the open-source and commercial versions of the DPC++ compilers. All examples in this book compile and work with either DPC++ compiler.

### Errata, Notes, Downloads, Feedback

Please check our "preview book" website for information including errata, updates, and downloads (includes all sample code): https://tinyurl.com/book-dpcpp

We will also list some additional resources as they become available. Your feedback is welcome. You can email James Reinders at dpc++@jamesreinders.com with any suggestions, encouragement, criticism, or questions that you may have. James will be sure to share any feedback that you send with all the authors.

### oneAPI

Visit <u>https://oneAPI.com</u> for information on the oneAPI. Find resources for software developers at <u>https://software.intel.com/oneAPI</u> — including the oneAPI toolkits, discussion forums, online training, event information, and more.

The oneAPI website hosts some training on oneAPI, which contains a number of training modules dedicated to DPC++. While we expect the book to dig deeper than the online classes in many respects, listening to the training should be a very useful companion to the book.

### **PREFACE FOR CHAPTER 1-4 PREVIEW**

The online training also explains how to register for an online account to access the tools already installed with access to CPUs, GPUs, and FPGAs.

### **Enjoy Learning DPC++ and SYCL**

It is our hope that our book supports and helps grow the SYCL community, as we help promote data parallel programming in C++ using the DPC++ compiler.

We wish you the best as you learn DPC++, and SYCL. We welcome your feedback. We hope you will enjoy this preview, and be watching for the full book, by mid-2020, available from Apress in print, and as a free download.

> Míchael Kínsner, James Brodman, John Pennycook, Xínmín Tían, Ben Ashbaugh, and James Reínders

> > November, 2019

## Introduction

We are very excited to be teaching data-parallel programming for C++ in this book through use of DPC++ and SYCL.

SYCL is an industry led, Khronos standard, for adding data parallelism to C++ for heterogeneous systems. We will define data parallelism, and heterogeneous systems, in the next few pages.

DPC++ is an extension of C++, incorporating SYCL and other new features. There is an open-source DPC++ compiler, initially created by Intel, available from a GitHub repository. There is a commercial version of the DPC++ compiler, augmented with additional tools and libraries for DPC++ programming and support, available from Intel.

All the features of DPC++, and SYCL, are supported by both the open-source and commercial versions of the DPC++ compilers. All examples in this book compile and work with either DPC++ compiler.

In this book we introduce DPC++ for the first time, while also being the first full book teaching SYCL.

It is our hope that this book supports and helps grow the SYCL community.

To avoid writing "SYCL and DPC++" or "DPC++ and SYCL" over and over in this book, we do two things:

(1) we speak of DPC++ in an inclusive manner, and

(2) we speak of SYCL features with the understanding they are always DPC++ features as well.

Most of the examples in this book should work with any up-to-date SYCL compiler including the DPC++ compilers. Early in each chapter we clearly state when extensions unique to DPC++ are used.

#### **DPC++ AND SYCL IN CHAPTER 1**

This chapter introduces DPC++ and SYCL. A box like this one, early in each chapter, will clearly state when extensions unique to DPC++ are used within the chapter. The sample code in this chapter does not use any DPC++ specific extensions.

DPC++ includes all of SYCL. When something is specific to only DPC++, we will go out of our way to be clear.

Our book will do considerably more than introduce — we will dive into the key issues and solutions that are encountered while constructing effective data-parallel programs, with C++, to program the powerful heterogeneous systems we have available today.

### What is Data-Parallel Programming?

DPC++ and SYCL are designed to encourage and support a data-parallel programming style, although they do not limit us to only data-parallel programming.

Data-parallel programming might be described as both a mindset, as well as a way of programming. Data is operated on in parallel by a collection of processing elements. Each processing element is hardware capable of some computation on the data. These processing elements may exist on a single device, or many devices in our computer systems. We specify our code to work on our data in the form of a *kernel*.

When programming in a data-parallel fashion, we focus on specifying what operations (written as a *kernel*) should apply to every data element. Data-parallelism applies best on regular data structures like arrays and matrices because they may offer many opportunities for parallel computations that are easy to specify.

An important concept in data-parallel programming is the kernel — a function that will be executed on a device containing processing elements. The term kernel is used in data-parallel programming including SYCL, OpenCL, CUDA, and DPC++.

In contrast, when programming in a task-parallel fashion, we specify a distribution of code among processing elements and then work to have the data travel to the computations as dictated by the code.

Parallel programmers generally use elements of both data-parallel and taskparallel programming, and therefore the features of DPC++ and SYCL are not all strictly data parallel only. One example is that SYCL allows running two *separate* submissions in parallel. Blending data-parallel programming and task-parallel programming is to be encouraged, and we hope that will seem natural and normal after reading this book. A "Think Parallel" mindset will remain critical to make the most of such knowledge — know where your parallelism is, and have a plan to exploit it!

DPC++ and SYCL are designed to encourage and support a dataparallel programming style, although they do not limit us to only dataparallel programming.

#### What are Heterogeneous Systems?

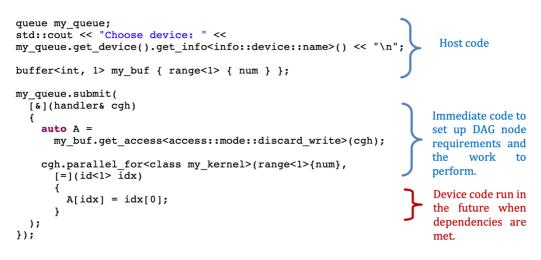

For our purposes, a heterogenous system is any system which contains multiple types of computational devices. For instance, a system with both a CPU (Central Processing Unit, often simply called a processor) and a GPU (Graphics Processing Unit, with computationally intensive versions often referred to as General-Purpose GPU, or GPGPUs) is a heterogeneous system. Today, the collection of devices includes CPUs, GPUs, FPGAs (Field Programmable Gate Arrays), DSPs (Digital Signal Processors), ASICs (Application Specific Integrated Circuits), and AI chips (graph, neuromorphic, etc.).

Having multiple types of devices, each with different architectures and therefore different characteristics, leads to different programming and optimization needs for each device. This creates a number of challenges —helping solve these being the motivation behind DPC++.

DPC++ exists to address the challenges of data-parallel programming for heterogeneous systems.

### Enjoy the Journey – This is something BIG

Seeking to support data parallelism for programming heterogeneous systems within C++ is no small vision. We hope you enjoy the journey as much as we do. The emergence of both open source, and commercial, support for SYCL and DPC++ is strong evidence that we are on the cusp of something big.

### Parallel Programming in C++

Parallel programming is a wide and complex topic – and we focus on a key aspect of it, namely language support for data-parallel programming. This is distinct from, and complementary to, the highly portable facilities of Threading Building Blocks (TBB) and today's C++ standard that address other key aspects of parallel programming. Language support for data parallelism is critical because it allows developers to express their data parallel algorithms more directly, and enables compiler optimization technologies. Prior efforts including OpenMP and OpenCL have given us substantial real-world experience upon which to build. That experience has led to a deep understanding of how critical it is to make data-parallel programming a first-class citizen in a programming language and support that directly with compiler technology.

DPC++ is modern C++.

DPC++ should feel familiar to C++11 programmers.

DPC++ will act as a proving ground for C++ features supporting heterogeneous platforms and parallelism.

DPC++ will provide valuable input to future ISO C++ standards.

### Journey to Parallelism, Scaling, Portability

Parallel programming has come a long way over multiple decades and we can now better assess the most effective ways to support data-parallel programming. The heterogeneous nature of today's computing systems must be accounted for as well. Being effective at both data parallelism and heterogeneous programming requires good solutions for scaling and portability. Real Estate is all about location, location, and location. Parallel Programming is all about scaling, scaling, and scaling.

Scaling is a measure of the effectiveness of parallel programming, which measures the degree to which a program effectively uses more parallel hardware when available. We must never lose sight of the objective, for any parallel programming system, to allow for effective scaling. This includes scaling as we move our application across platforms. Heterogeneous platforms confound the problem because different architectures can have substantially different needs. We do not pretend that DPC++ solves scaling and all heterogeneous platform needs for us. Rather, DPC++ is a tool that allows us to succeed by helping us to deal with issues that would otherwise interfere with our scaling goals, and by offering us techniques to address the needs of heterogeneous platforms. That may sound easier than it is; that DPC++ succeeds at this is quite an accomplishment.

DPC++ forms a solid foundation on which to build scalable portable applications.

Portability is a complex topic and includes the concept of *functional portability* (the program works) as well as *performance portability* (the program achieves high performance when ported to a new machine). DPC++ addresses both by giving us, as programmers, the tools we need to succeed. DPC++ does not magically make the issues disappear — DPC++ forms a solid foundation on which to build portable applications that also scale. Not every program can scale, but DPC++ helps us when they can — and even then, we are responsible for devising an effective plan for performance portability ourselves as programmers.

Constantly question your own approaches with respect to their impact on both scaling and the multiple facets of portability.

We will touch on scaling and performance portability throughout this book. We will teach to reinforce both capabilities, usually without dwelling on them specifically. We encourage you to constantly question your own approaches with respect to their impact on both scaling and the multiple facets of portability for your own applications.

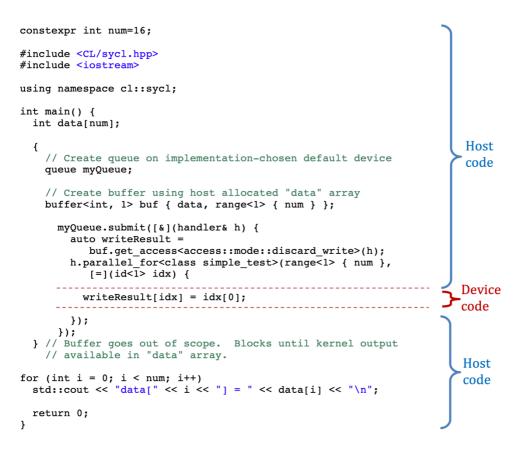

### First look at DPC++ code

Figure 1-1 shows a sample SYCL program. In this example, only a short segment of code is destined to run on a *device* (the default accelerator if one exists on the system, or the host via the always available *host device* if no accelerator is present). Coding in DPC++ or SYCL has a "single source" property, which means that host code and device code can exist within the same source file. This is illustrated in the example in Figure 1-1. Supporting single source allows host and device code to be easily considered, and also optimized, together by a compiler. This, it turns out, is a critical advantage in using DPC++ or SYCL. DPC++ and SYCL also allow for compilation of the device code to be completed at runtime for more flexibility. Even in such a case, significant optimization can occur, in advance, during the compilation of the application. We will discuss this more in an upcoming section on the Compilation Model.

In Figure 1-1, the motivations for chapters 2, 3, 4 are highlighted. Chapter 2 will describe how to control *where* our code runs — in other words, on what device(s) code will run. Chapter 3 will describe how to manage data effectively — so that it shows up where and when it is needed. Chapter 4 will describe how to write kernels — the essence of code to be run on a device. Additional chapters follow to expand on the basics learned in the first four chapters.

### Why DPC++?

There are several reasons that DPC++ is needed, and is the right answer for us today:

- We need to address the critical need for supporting data-parallel programming as a first-class citizen it needs to be portable, high-level, and non-proprietary while addressing modern heterogeneous computer architectures.

- We want the same programming environment across host and device code: support for modern C++ features (in particular, templates), better type safety, and for data parallel code to look and feel like sequential code.

• The future of computer architecture includes accelerators that span scalar, vector, matrix, and spatial (SVMS) operations (coming up in Figure 1-2); support for heterogeneous machines including the SVMS capabilities are needed. Support should span highly complex and programmable devices, as well as fixed function or specialized devices that are less programmable.

```

#include <CL/sycl.hpp>

#include <iostream>

#include <array>

#define SIZE 1024

using namespace cl::sycl;

int main() {

std::array<int, SIZE> a, b, c;

for (int i = 0; i<SIZE; ++i) {</pre>

a[i] = i;

b[i] = -i;

c[i] = i;

}

range<1> a_size{SIZE};

auto platforms = platform::get platforms();

for (auto &platform : platforms) {

std::cout << "Platform:</pre>

<< platform.get info<info::platform::name>() << std::endl;

auto devices = platform.get devices();

for (auto &device : devices ) {

std::cout << " Device: "</pre>

<< device.get_info<info::device::name>()

Chapter 2:

<< std::endl;

controlling

}

where

}

queue d queue;

device code

buffer<int, 1> a_device(a.data(), a_size);

will be run

buffer<int, 1> b_device(b.data(), a_size);

buffer<int, 1> c_device(c.data(), a_size);

Chapter 3:

d_queue.submit([&](handler &cgh) {

sharing

auto c res =

c device.get access<access::mode::write>(cgh);

data within

auto a in =

the system

a_device.get_access<access::mode::read>(cgh);

auto b in =

b device.get access<access::mode::read>(cqh);

cgh.parallel for<class ex1>(a size,[=](id<1> idx) {

Chapter 4:

c res[idx] = a_in[idx] + b_in[idx];

writing

});

device

});

code

}

}

```

*Figure 1-1: First look at DPC++/SYCL programming*

- When targeting multiple architectures (e.g., CPUs., GPUs, FPGAs), access to performance is important even if it takes programmer effort. Hiding the controls where a programmer cannot access them is unacceptable.

- Programming should expose higher level abstractions and language mechanisms than those presented by OpenCL or CUDA, and in a non-proprietary form. Doing so will give us higher programmer productivity and lower the barrier to entry for new programmers.

DPC++ addresses all of these needs. DPC++ serves as an open alternative to proprietary, device-specific languages.

#### Why must it be a first-class citizen?

We use the phrase 'first-class citizen in the language' to express a need that the features we discuss be a known part of the language, so that it is both portable and can be well supported (and especially optimized!) by a compiler.

A compiler "knowing" SYCL and DPC++ will always be able to generate parallel code more effectively than a pure template library approach. However, we must note that SYCL and DPC++, are technically implementable as template libraries. They do not rely on new keywords or syntactic changes to C++. Nevertheless, effective implementations of DPC++ or SYCL *do* require compile support and a tuned runtime. This differs from Threading Building Blocks (TBB), which relies only on its template implementation and does not require modified compilers for performance. The DPC++ approach is similar to OpenMP, which will compile with any compiler, but will not yield benefits without an optimizing compiler that "knows" OpenMP.

Standardization into a language such as C++ is a long and careful process with constraints aimed to ensure a consistent experience far into the future. We hope that DPC++, and readers of this book, will provide valuable input into this process.

## Made for each other: Data parallelism and Big Data

In addition to discussing how to program and control devices, we will also discuss data management repeatedly throughout this book. This is because assigning work to a device is complicated by data, beyond simply saying "do the work over there!" Data movement costs time and power and has to be managed as a first-class citizen. With data parallelism,

we are likely to manage a *lot* of data (think "Big Data"), so this is not a trivial concern. We cannot afford to behave like the proverbial ostrich sticking its head in the sand hoping all the data movement will be optimally handled with no effort from us. On the other hand, we hope that much of it is automatic so we can focus our programming where it matters most.

Data parallelism and Big Data go hand-in-hand; data movement costs time and power, and has to be managed as a first-class citizen.

### SYCL, DPC++, C++

The focus of this book is "Data-Parallel C++" and it is realized via "SYCL with extensions." Please allow us to explain.

### Khronos SYCL

SYCL (pronounced 'sickle') represents an industry standardization effort that includes support for data-parallel programming for C++. It is summarized as "C++ Single-source Heterogeneous Programming for OpenCL." The SYCL standard, like OpenCL, is managed by the Khronos Group.

SYCL is a cross-platform abstraction layer that builds on OpenCL. It enables code for heterogeneous processors to be written in a "single source" style using C++. This is not only useful for us as programmers, but it also gives a compiler the ability to analyze and optimize across the entire program regardless of the device on which the code is to be run.

Unlike OpenCL, SYCL includes templates and lambda functions to enable higherlevel application software to be cleanly coded with optimized acceleration of kernel code. Developers program at a higher level than OpenCL but always have access to lower-level code through seamless integration with OpenCL, as well as C/C++ libraries.

### DPC++

In order to fully address the needs of C++ programmers, a number of features are needed that are not currently within SYCL. For now, critical support for Unified Shared Memory (USM), and subgroups, exist only in DPC++.

The extensions we include in DPC++, to the extent they can be applied across many platforms, may be submitted for consideration in future SYCL specifications. We

cannot guarantee that they will be incorporated, or be unchanged. We do work hard in the SYCL community, and in our book, to minimize the need for changes.

DPC++ includes *all* of SYCL. We may not dive into all aspects of DPC++ and SYCL in this book because our focus is teaching effective data-parallel programming. Regardless, all of SYCL is included in DPC++ and so these features are available even if not mentioned in this book.

While we teach DPC++ and SYCL in this book – we do not intend this book to be an exhaustive reference for all capabilities.

We focus on DPC++ and SYCL features (including extensions) that teach effective data-parallel programming.

For the parts of DPC++ which are SYCL features, we will describe them as SYCL features. For any extensions, which are not part of the SYCL specification at the time we write this (SYCL 1.2.1r5), we will not label them as SYCL features. Of course, the SYCL standard will evolve and may incorporate a feature in the future that will not be labeled as SYCL in this book because of the timing.

Each chapter in this book includes a summary box near the beginning of the chapter as shown next. It is possible that by the time you read this book, some features we call out as unique to DPC++ may have been incorporated in some form by a future SYCL standard. We encourage you to browse our online errata (see Preface and Epilogue for URL), where we plan to make notes about such developments.

#### **DPC++ AND SYCL IN CHAPTER X**

Features that are discussed, but unique to DPC++ are called out clearly.

Otherwise, most or all of each chapter will be SYCL features and will entirely be included in DPC++.

#### C++

C++ lacks direct support for data parallelism in the language, and it lacks the controls needed for modern heterogeneous systems. We expect consensus to grow on the need and

the methods to solve these challenges. Therefore, you can see why we say that the focus of this book is "Data-Parallel C++" and it is realized via "SYCL with extensions."

Like the rest of the SYCL community, we hope many of the key features of SYCL will be considered for future C++ standards. Time will tell.

### Why Heterogeneous Systems?

Heterogeneous computing matters as computer architects work to limit power consumption, reduce latency, and increase throughput. From the early 1990s until 2006, a so-called "free lunch" (continual performance boosts to virtually all applications) existed because processor performance was reliably doubling every two to three years, mostly because clock rates were doubling every couple of years. That era ended around 2006, and a new era of multicore and then many core processors emerged. The architectural shift to parallel processing gave multitasking systems a boost but did not give most existing *single* applications a performance boost without alterations in programming. This new era also saw accelerators, such as GPUs, gain popularity for accelerating more parts of applications than ever before. That gave rise to an era of heterogeneous computing, and a deluge of proposed accelerators with their own specialized processing capabilities, and with many different programming models.

Trading Generality for Performance: Architects of Accelerators boost performance for specific algorithms by reducing generality.

By being more specialized, accelerator designs can offer higher performance on specific problems because they do not have to be designed to handle every problem. This is a classic computer architecture trade-off. This generally means accelerators can only support subsets of the programming languages that were designed for processors. In fact, in DPC++ only code written in a kernel can be targeted to an accelerator. As we will see in Chapter 4, kernel code has some restrictions on it that do not exist for C++ code in general. Worrying about these restrictions would be a needless distraction because the uniqueness of each accelerator should be on our minds as programmers.

We need to think about the programming model, formulation of algorithms, and the types of workloads that an accelerator will perform well on.

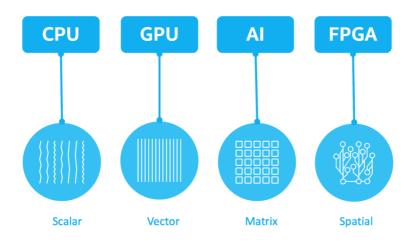

Accelerator architectures can be bucketed into broad categories that impact how we need to think about the programming model, formulation of algorithms, and the types of workloads that an accelerator will perform well on. Like all attempts to categorize, there are many possibilities. Figure 1-2 utilizes a taxonomy of Scalar, Vector, Matrix, and Spatial (SVMS).

CPUs are the best choice for general purpose code including scalar and decision making (frequently branching) code, and often have built in accelerators for vectors. GPUs seek to accelerate vectors, and the closely related tensors. DSPs seek to accelerate specific mathematical operations with low latency, often in designs dealing with analog signals such as a cellphone. Accelerators for AI generally seek to accelerate matrix operations, although some may accelerate graphs as well. FPGAs and ASICs are particularly suited to accelerate spatial problems, including problems expressed in terms of flow graphs or pipelines.

While these buckets may be as good as any, they are only rough buckets for thinking — they are certainly not absolute rules. We can note that virtually all modern

processors have some form of vector, or even matrix, support. The point of Figure 1-2 focuses more on observations about unique advantages, such as the fact that processors can prove uniquely capable at scalar when accelerators falter. Categorization can be useful for thinking, but we should not get hung up on them too much.

### **Platform Model**

The platform model, used by SYCL and DPC++, specifies a host that coordinates and controls the compute work that is performed on the devices. A device is an accelerator, presumably with specialized capabilities. Chapter 2 describes how to assign work to devices, and Chapter 4 dives into how to program devices.

As we discuss in Chapter 2, there is always a device corresponding to the host, known as the *host device*. Providing this guaranteed-to-be-available target for device code allows device code to be written assuming at least one device is available, even if it is the host itself! The choice of the devices on which to run device code is under program control — it is entirely our choice as programmer if, and how, we want to execute code on specific devices.

Amdahl's Law is a formula to predict the theoretical speedup when using multiple processors to do a fixed workload. Maximum gain from parallelism is limited to (1/(1-p)) where p is the fraction of the program that runs in parallel (e.g.,  $2/3^{rd}$  run in parallel, limits speed-up to 3X).

We must take care in our program to overlap work in the system as well as to hide latencies caused by data movement. Otherwise, using the host to dispatch work serially can become a serious performance bottleneck due to Amdahl's Law. This is why the programming model has us queue work to a device and not idly wait for its conclusion, gives methods to describe dependencies between work items, and provides numerous data management capabilities. These help to lower the time spent outside of parallel execution, as well as to free the host for doing important work itself. The most effective programs make efficient use of both the host and devices to get work done.

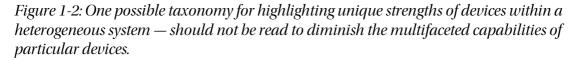

#### Multiarchitecture (aka "Fat") Binaries

Since our goal is to have a single source code to support a heterogeneous machine, it is only natural to want a single executable file to be the result.

A multiarchitecture binary (also called a *fat binary*) is a single binary file that has been *fattened* (expanded) to include all the compiled and intermediate code needed for our heterogeneous machine. A multiarchitecture binary acts like we are used to having an a.out, or A.EXE, operate for us — but it contains everything needed for a heterogeneous machine. This helps automate the process of picking the right code to run for a particular machine. As we discuss next, one form of the device code in a fat binary is an intermediate form that defers the final code creation until runtime.

### **Compilation Model**

The single source nature of SYCL and DPC++ allows compilation to "just work." In other words, we do not need to know all the details of how it works because of the similarity to a standard C++ compilation.

Since the compilation model supports code that executes on both a host and potentially several accelerators simultaneously, the commands issued by the compiler, linker, and other supporting tools are more complicated than the C++ compilations we are used to (targeting only one architecture). Welcome to a heterogeneous world!

While this complexity is hidden from us by default and "just works," advanced users may want to understand these details to better target specific architectures.

In particular, compiling for multiple architectures presents several challenges, particularly because some may be known and some unknown at the time of compilation.

The DPC++ compiler can generate target-specific executable code similar to traditional C++ compilers (*ahead-of-time* compilation, sometimes referred to as 'offline kernel compilation'), or it can generate an intermediate representation that can be *just-in-time* compiled to a specific target at run time.

#### DPC++ compilation can be "ahead of time" or "just in time."

By default, when we compile our code (for most devices), the output for device code is in an intermediate form. At runtime, the device handler on the system will *just-in-time* compile the intermediate form into code to run on the device(s) to match what is available on the system.

We can ask the compiler to compile ahead-of-time for specific devices, or class of devices, in advance. This has the advantage of saving runtime, but it has the disadvantage of added compile time and fatter binaries! Compiling for a specific device ahead-of-time also helps us check at build time that our program should work on that device. With just-in-time, it is possible that a program will fail to compile for a specific device only when we try to run on it if device code uses features that are only optionally exposed by devices such as images.

Figure 1-3 illustrates the compilation process from source code to fat binary (executable). Whatever combinations we choose are bundled together in a fat binary. The fat binary is employed by the runtime when the application executes and the particular form needed for the target device is determined at runtime.

*Figure 1-3: Compilation process showing ahead-of-time and just-in-time options using fat binary (executable).*

## Truth and Fallacy of Write Once, Run Everywhere

When we consider real heterogeneous systems, we might notice that the accelerators are there for specific reasons. The accelerators are not added into a computer design in order to run all the code, and in systems with multiple accelerators they are not there to be redundant with each other.

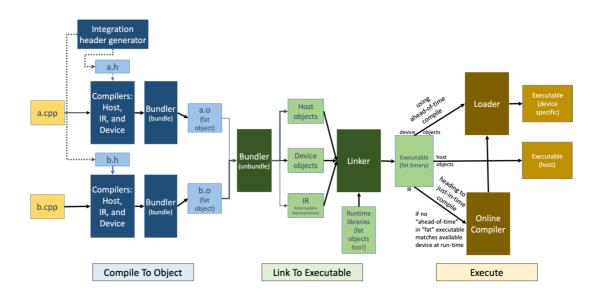

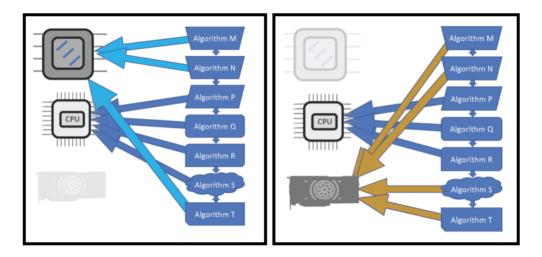

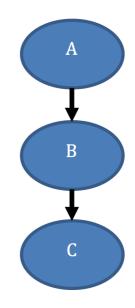

A single application may use multiple accelerators, but with specific purposes for each. This gives rise to two different usage scenarios to consider (illustrated in Figure 1-4 and Figure 1-5), both of which are equally well supported by DPC++.

In Figure 1-4, we consider that an application may use different algorithms that may be designed to perform on a particular type of accelerator if present. Such a program can run everywhere, and the CPU is used unless a well-suited accelerator is available for a particular algorithm. However, we do not try to make each algorithm run efficiently on all possible accelerators. While DPC++ code will be able run on all accelerators, there are options for "fallback" if and when an accelerator does not support a particular feature. We discuss coding for "fallback" in Chapter 2.

Figure 1-4: Left: Fallback on Host (CPU) if no device present, Right: Offload different algorithms to the devices with best match for the needs of each algorithm.

In Figure 1-5, we consider that some algorithms may be suitable for acceleration on a variety of devices. Inferencing, for instance, might be suitable for different accelerators — perhaps offering different tradeoffs in latency, performance, and power consumption. Again, such a program can be designed to run everywhere and the particular algorithm may be suitable for multiple accelerators. Even in this case, making each algorithm run efficiently on many different accelerators is likely to be a complex task.

Figure 1-5: Left: the top device can serve the needs of Algorithms M, N, and T; Right: The bottom device can serve the needs of Algorithms M, N, S, and T. If both devices, or neither, are present then refer to Figure 1-4.

### **Direct programming**

In our two scenarios illustrated in Figure 1-4 and Figure 1-5, we can write our code once and let the compiler translate it for each accelerator. However, it is unlikely that a single coding will run efficiently on all accelerators when you consider the variety of architectures that give rise to accelerators being interesting in the first place! As we illustrated in Figure 1-2, specific accelerators excel at specific styles of algorithms. Therefore, DPC++ gives us a way to specify different coding for different accelerators when we want to do so. This is called direct programming. As we will show in Chapters 13, 14, and 15, this direct programming is primarily motivated by architecture of a particular class of accelerator, and only a little by vendor specific features. In other words, coding for GPU is largely an exercise to aligning to the style of processing GPUs excel at doing, and coding for an FPGA is largely an exercise in aligning to the strengths of an FPGA. Of course, for the case that an accelerator is not always present we want to use the full capabilities of the CPU which may require we not rely on a version specifically optimized for an accelerator.

Using direct programming is necessary because compilers simply do not perform algorithm conversions.

Using direct programming is necessary because compilers simply do *not* perform algorithm conversions. For instance, if we code a *bubble sort* (not a great sorting algorithm in general) we do not expect the compiler to refactor the code into a quicksort (generally considered a very good sort algorithm). Instead, it is our job as programmers to either code a *quick sort*, or to use a library routine called 'sort' and hope it uses the best algorithm.

Compilers do not convert a bubble sort algorithm to a quick sort algorithm for us. That is our job as programmers. Likewise, a completely generic matrix multiply will not be compiled into an optimized matrix multiply for a GPU.

Similarly, DPC++ gives us the opportunity to use coding styles aligned with the accelerator we anticipate using, or to use a different aspect of oneAPI and leverage APIs (e.g., library functions) that are supported across multiple different architectures.

### Why Data Parallelism?

Data parallelism is one of the most important forms of parallelism for a parallel programmer to exploit. In practice, with a good data-parallel programming model, one can achieve high degrees of *scaling*. Scaling refers to a desire to see performance increase (scale up) when compute resources increase (scale up).

Effective parallel programming is all about *scaling*. If we expand our computing resources by 100X, ideally, we hope our application will run a hundred times as fast. Of course, there are complications — chief of which is expressed by Amdahl's Law.

### Think (Data) Parallel

Effective parallel programming starts with a clear vision, by the programmer, of where the parallelism is. That is followed by a strategy on how to exploit the parallelism in a manner that yields speed-up. Learning to be an effective parallel programmer rests squarely on developing a knack for finding the best way to break up a problem into a large number of independent tasks. Independence is critical, because interaction between tasks will limit scaling — interaction is effectively a serialization, and Amdahl's Law tells us that will limit us.

Data parallelism, in practice, tends to work very well for parallel programming. If we can figure out a kernel of computation that we want to apply on all of our vast data, we can see amazing speed-ups in our applications. The two key concepts in our favor here are:

- Independence: Thinking in terms of *kernels* encourages exactly the sort of independence we need in our strategy to achieve high scaling.

- Scale with problem size: problems that involve processing data will scale with the problem size when we have independence. This is wonderful because tackling bigger data sets, or otherwise finding more Big Data, is not considered hard to do these days!

### Intranode, not multinode, parallelism

DPC++ is focused on parallelism within a single node, often call intranode parallelism. A node, in this case, is defined as scope for the DPC++ host with its attached devices. The host may be a single, or multiple, CPUs for instance — a node is the shared memory environment of those one or more CPUs with attached accelerators (DPC++ devices). The topic of multinode parallelism (parallel programming often associated with MPI – which connects nodes together to operate in parallel), is not directly addressed by DPC++, SYCL, or OpenCL. Multinode, in our context, would be a collection of multiple hosts. Mechanisms to allow efficient multinode parallelism are present in DPC++, SYCL, and OpenCL. Multinode parallelism with DPC++, for instance, could use MPI to orchestra multiple nodes each running DPC++ in a fashion learned from this book. Multinode parallelism is beyond the scope of this book.

### **Other Accelerator Programming Models**

The concept of accelerators in computing is not a new one, and over the decades they have been accompanied with a wide variety of programming models. Early floating-point processors were programmed separately, and even the introduction of float-point for x86 processors occurred as a coprocessor with a distinct set of instructions that were executed outside the processor but with memory accesses coordinated by the processor.

Having accelerator programming in the same high-level programming language has been a goal of many modern programming environments. The end of rising clock rate (circa 2006) has given rise to many new accelerators and interest in programming them more easily and effectively.

Rather than look at a historical view of accelerator models, we have chosen to briefly list ones with the most contemporary relevance and offer a few notes on how they relate to DPC++, and in some instances oneAPI.

**oneAPI**: An Intel-led initiative to provide a common support model for accelerators regardless of programming language. First public beta Q4 2019. <u>http://software.intel.com/oneAPI</u>

**DPC++** (Data-Parallel C++): consists of C++ with SYCL and extensions, the subject of this book. DPC++ outfits C++ for data parallelism. DPC++ supports the execution of compute kernels. First public beta Q4 2019. <u>http://software.intel.com/oneAPI</u>

**SYCL**: also the subject of this book, a Khronos specification for extending C++ with a cross-platform abstraction layer. SYCL offers a higher-level programming interface for OpenCL devices. SYCL enables code for heterogeneous processors to be written in a "single-source" style using C++. The SYCL standards team enjoys widespread participation. SYCL supports the execution of compute kernels. First specification May 2015. <u>https://www.khronos.org/sycl/</u>

**OpenCL** (Open Computing Language): a Khronos specification for a framework for writing programs that execute across heterogeneous platforms including CPUs, GPUs, DSPs, FPGAs, etc. Most vendors participate in the OpenCL standards body. Such broad support for OpenCL has resulted in the broadest list of accelerator devices being supported of any accelerator programming system. OpenCL focuses on support for the execution of compute kernels. First specification in August 2009. <u>https://www.khronos.org/opencl/</u>

**CUDA** (Compute Unified Device Architecture): A programming model for "CUDA enabled" Nvidia GPUs. The CUDA platform is a software layer to connect with the virtual instruction set of a large range of Nvidia GPUs in order to execute compute kernels. Initial release in June 2007. <u>https://developer.nvidia.com/cuda-zone</u>

**TBB** (Threading Building Blocks): An Intel-led open-source project that adds support for parallelism to C++ through template libraries. The most popular abstract programming model for parallel programming in C++, and is supported on all modern systems. Does not itself implement SIMD or vectorization support — rather than duplicate such efforts it relies on compiler extensions (OpenMP, OpenCL, SYCL, DPC++) for that. Support for heterogeneous systems is achieved through the ability to offload functionality within a TBB flow graph using other models such as OpenCL, CUDA, SYCL, or DPC++. Initial release in mid-2006. https://github.com/intel/tbb

**OpenMP** (Open Multiprocessing directives): A specification for a set of compiler directives, library routines, and environment variables that can be used to specify high-level parallelism in Fortran, C, and C++ programs. Vendors and HPC users participate in

the OpenMP standards body. OpenMP is the most widely adopted standard for systems, has been implemented by all major compiler vendors, and is supported on all modern systems. First specification in late 1997. <u>https://www.openmp.org/</u>

**OpenACC** (Open Accelerator directives): A specification for a set of compiler directives, library routines, and environment variables that can be used to specify high-level parallelism in Fortran and C program — developed as an offshoot of OpenMP by Cray, CAPS, Nvidia and PGI to address the needs of Nvidia GPUs. OpenACC adopted a more compiler-friendly descriptive specification, versus the more user-friendly prescriptive specifications of OpenMP. Initial specification November 2011. Cray announced, in 2019, plans to phase out OpenACC support in favor of the unified OpenMP support for heterogeneous systems. <u>https://www.openacc.org/</u>

**C++ AMP** (C++ Accelerated Massive Parallelism) is a library implemented on DirectX 11 and an open specification from Microsoft for implementing data parallelism using GPUs directly in C++. C++ AMP provides a single-source way to write programs that compile and execute kernels on GPU data-parallel hardware. First specification August 2012. <u>https://docs.microsoft.com/cpp/parallel/amp/cpp-amp-overview</u>

**AMD HCC** (Heterogeneous Compute Compiler): single source C++ with code generation to both x86 processors and *HSAIL* (heterogeneous offload to AMD APUs and discrete GPUs via *HSA* enabled runtimes and drivers). *HSAIL* is short for HSA Intermediate Language. *HSA* is short for Heterogeneous System Architecture. HSA is a set of specifications, initially created by AMD, that allows for the integration of central processing units and graphics processors on the same bus, with shared memory and tasks. First specification March 2015. <u>https://gpuopen.com/compute-product/hcc-heterogeneouscompute-compiler/</u>

**Kokkos** (C++ Performance Portability Programming EcoSystem): a project from Sandia National Labs; Kokkos provides abstractions for both parallel execution of code and data management with the stated objective to implement a programming model in C++ for writing performance portable applications targeting all major HPC platforms. First released in 2008 as a collection of the handful of sparse and dense kernels as part of the Trilinos Project at Sandia, it has developed notoriety in its innovations for heterogeneous support over the years since. <u>https://github.com/kokkos</u>

**RAJA**: a collection of C++ software abstractions, being developed at Lawrence Livermore National Laboratory (LLNL). RAJA makes heavy use of C++ templates and is best when C++ lambda expressions are used to express the computational kernels. CHAI is a closely related library that complements RAJA by providing pointer abstractions that hide run-time data copies that move kernel data to execution memory spaces as needed. Umpire is a closely related library that provides a simple, unified interface to access

capabilities for memory resources. Described in 2014, first release 2016. https://github.com/LLNL/RAJA

**MPI** (Message Passing Interface): widely used and supported standard for portable message-passing on parallel computing architectures. Many vendors and major HPC users participate in the MPI standards body. MPI defines the syntax and semantics of a core of library routines to enable writing portable message-passing programs in C, C++, and Fortran. There are several well-tested and efficient implementations of MPI, many of which are open-source or in the public domain. First draft specification in 1992, 1.0 released in 1994. <u>https://www.mpi-forum.org/</u>

### **Evolution of SYCL (thus far)**

What we know of as SYCL today started as the "High Level Model for OpenCL" (HLM for OpenCL) in 2010 when some members of the OpenCL working group wanted to develop a higher-level interface to target OpenCL devices. A sub-group was formed to study what could be done to provide a "high-level programming model, unifying host and device execution environments through language syntax for increased usability and broader optimization opportunities."

Early SYCL implementations relied on utilizing OpenCL to reach accelerator devices. However, SYCL has proven to be a more general heterogeneous framework able to target other systems. For example, the ComputeCpp and hipSYCL implementations each target Nvidia GPUs by outputting to CUDA, and hipSYCL targets AMD GPUs by outputting to AMD HIP on the ROCm platform.

### March 2015 – SYCL 1.2

The first release of a specification from The Khronos Group was called SYCL 1.2 in March 2015. SYCL continues as a complementary effort alongside the ongoing evolution of the OpenCL language. SYCL 1.2 built on the features of C++11.

SYCL generated a lot of interest and support, largely among tool and framework creators. For instance, Tensorflow targeting of OpenCL has been implemented by using SYCL. Multiple efforts to develop compilers and tools for SYCL arose based on SYCL 1.2.

However, for application writers, SYCL really starts with 1.2.1r5.

### April 2019 – SYCL 1.2.1r5

On April 18, 2019, SYCL 1.2.1 revision 5 became the latest SYCL based on OpenCL 1.2, and (despite the slight change in numbering) was a *major* update representing four years of efforts by the SYCL group. Khronos created an open-source project, hosted on github, to support Parallel STL on top of SYCL, running on OpenCL devices. The SYCL conformance test suite (CTS), an open-source project on github, was also introduced to help vendors test compliance. The announcements from Khronos noted that *SYCL brings the power of single-source modern C++ to the OpenCL and SPIR world, it also prepares the convergence with other standards such as ISO C++, and Khronos' Vulkan, OpenVX, and NNEF.*

### SYCL 1.2.1r6 and beyond

Revisions to the 1.2.1 standard are needed to clarify or adjust the standard. In particular, implementers of the standard are finding opportunities for clarifications, refinements, and corrections. While these do not materially impact the intent of SYCL, they will impact some topics within this book. We have endeavored to be current with the specification at time of publication — but changes are inevitable. We encourage the reader to visit our web site (https://tinyurl.com/book-dpcpp) for errata notes that will include notes when an adjustment is needed because of a standard revision.

### **SYCL Provisional 2.2**

An early and provisional SYCL 2.2 was previewed in May 2016 targeting C++14 and OpenCL 2.2. As related on Wikipedia, the SYCL committee decided to not finalize this version and is working on a more flexible SYCL specification to address the increasing diversity of current accelerators.

The SYCL committee actively engages and examines proposals for future SYCL features. Intel, as a member of the SYCL standard committee, is open about experiences extending SYCL with DPC++ features. It is logical to hope that those experiences will lead to further refinements to SYCL in the future.

### Summary

This chapter provided a base rationale for DPC++ and SYCL. Next, we will consider accelerators as devices. Such devices need to be given work to do (send code to run on them), be provided with data (send data to use on them), and have a method of writing

code (kernels). We will devote Chapters 2, 3, and 4, respectively, to expanding on facets of these three needs.

#### FOR THIS BOOK PREVIEW (CHAPTERS 1-4): ERRATA, NOTES, DOWNLOADS, FEEDBACK, ETC.

Please check our "preview book" website for information including errata, updates, and downloads (includes all sample code): https://tinyurl.com/book-dpcpp

We will also list some additional resources as they become available.

Your feedback is welcome. You can email James Reinders at dpc++@jamesreinders.com with any suggestions, encouragement, criticism, or questions that you may have. James will be sure to share any feedback that you send with all the authors.

Of course – watch for the full book, by mid-2020, available from Apress (no charge for PDF for the completed book, print copies will be available too).

https://tinyurl.com/book-dpcpp

# Where Code Executes

SYCL provides a heterogeneous programming framework in which code executes on a mixture of a host CPU and one or more devices. In such a framework, the mechanisms used to select the destinations for code execution are a fundamental part of the solution. This chapter describes where code can execute, introduces when it will execute, and describes the mechanisms used to control the locations of execution. Chapter 3 will describe how to manage data so it arrives where we are executing our code, and then Chapter 4 returns to the code itself and discusses the writing of kernels. These chapters combine to teach the fundamentals of writing a SYCL application, because before writing data parallel code in Chapter 4, we first need to understand the assignment of code to targets (this chapter) and the management of data (Chapter 3).

#### **DPC++ AND SYCL IN CHAPTER 2**

Everything discussed in this chapter is SYCL and is therefore fully supported by DPC++.

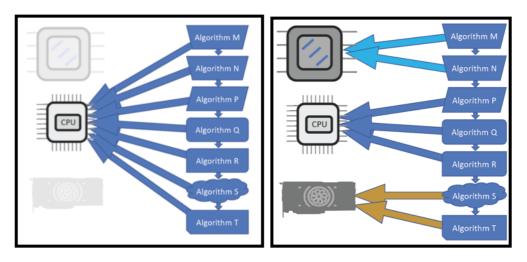

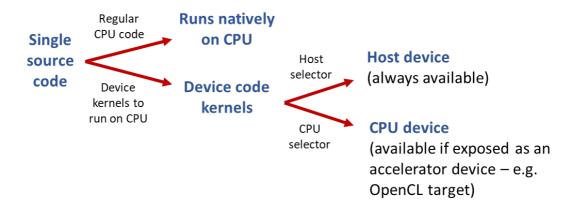

### Single source

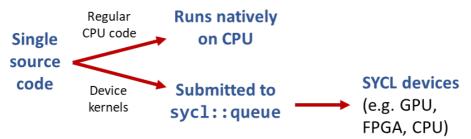

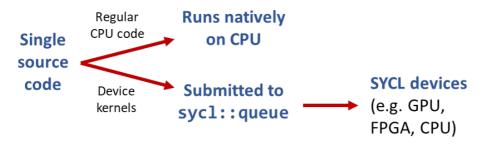

SYCL programs can be single source, meaning that the same file contains both the code that defines the compute kernels to be executed on SYCL devices and also the host code that orchestrates execution of those compute kernels.

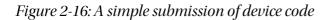

Figure 2-1 shows these two code paths graphically, and Figure 2-2 provides an example SYCL application with the host and device code regions marked.

#### CHAPTER 2 Where Code Executes

Combining both device and host code into a single source file can make it easier to understand and maintain a heterogeneous compute application. The combination also provides improved language type safety and can lead to additional compiler optimizations.

Figure 2-1: SYCL single source code contains both host code that runs natively on the host CPU, and device code that is executed on SYCL devices.

Figure 2-2: A simple SYCL program.

### Host code

SYCL applications contain C++ host code which is executed by the CPU(s) on which the operating system has launched the SYCL application. Host code is the backbone of a SYCL application in that it defines and controls the execution of compute on available devices. It is also the interface through which users define the data and dependencies that should be managed by the SYCL runtime.

SYCL host code is standard C++11 and SYCL-specific constructs and classes are designed to be implementable as a C++ library. This makes it easier to reason about what is allowed within host code (anything that is allowed in C++), and can simplify integration with build systems.

The host code in a SYCL application orchestrates data movement and compute offload to devices, but can also perform compute-intensive work itself, and can use libraries like any C++ application.

## Device code

Devices correspond to accelerators or processors that are conceptually independent from the CPU that is executing SYCL host code (the host processor). A SYCL implementation may expose the host processor also as a device, as described later in this chapter, but the host processor and devices should be thought of as logically independent from each other. The host processor runs native C++ code, while devices run device code.

SYCL queues are the mechanism through which host code submits work to a device for future execution. There are three critical properties of device code to understand:

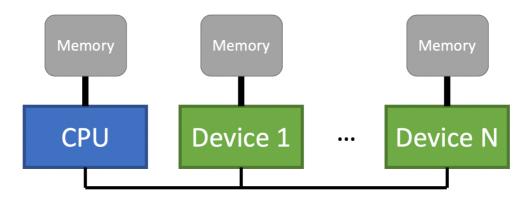

It executes asynchronously from the host code. The host program submits device code for future execution on a device, and the SYCL runtime tracks and initiates that work only when all dependencies for execution are satisfied (more on this in Chapter 3). The host program execution carries on before the submitted work is initiated on a device, providing the property that execution on devices is asynchronous to host program execution, unless the developer explicitly ties the two together.

- 2. There are restrictions on device code to make it possible to compile and achieve performance on accelerator devices. For example, C++ exceptions and run time type information (RTTI) are not supported within device code, because they would lead to performance degradation on many modern accelerators. The small set of device code restrictions are covered in detail in Chapter 10.

- 3. Some functions and queries defined by SYCL are available only within device code, because they only make sense in that context. For example, work item identifier queries that allow an executing instance of device code to query its position in a larger data parallel range (described in Chapter 4).

## Choosing a device on which to execute

To explore the mechanisms that control where device code executes, we consider five use cases:

| Method#1: | Running device code "somewhere", with the developer not caring which       |

|-----------|----------------------------------------------------------------------------|

|           | device it ends up being. This is often the first step in application       |

|           | development, because it requires the least code.                           |

| Method#2: | Explicitly running device code on the host device, which is typical used   |

|           | for debugging and is guaranteed to be always available on any system.      |

| Method#3: | Dispatching device code to a GPU or another accelerator device.            |

| Method#4: | Dispatching device code to a heterogeneous set of devices, such as a       |

|           | GPU and an FPGA.                                                           |

| Method#5: | Selecting specific devices from a more general class of devices, such as a |

|           | specific type of FPGA from a collection of available FPGA devices.         |

|           |                                                                            |

Developers will typically debug their code as much as possible with Method#2, and only move to Methods 3-5 when code is proven as much as it can be with Method #2.

# Method#1: Just run on a device (don't care what type)

By design, SYCL makes it easy to run device code on a device chosen by the runtime. This automatic selection of an available accelerator is designed to make it easy to start writing and running device code, where the developer doesn't yet care about what device is chosen. This device selection does not take into account the code to be executed, so should be considered an arbitrary choice.

To talk about choice of a device, even one that the implementation has selected for the user, it's important to first introduce the primary mechanism through which the program interacts with a device: the queue.

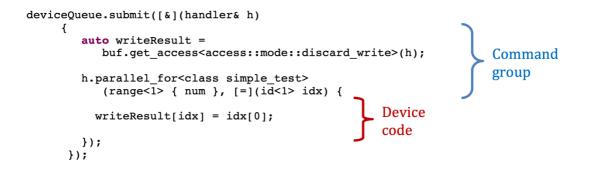

## Queues

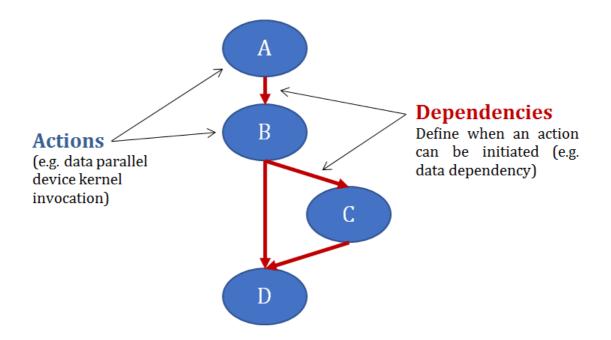

A sycl::queue is an abstraction to which work is submitted for execution on a single device. This work is most commonly the invocation of a data parallel computation, although other commands are also available such as for manual control of data motion, where the user wants more control than the automatic data movement provided by the SYCL runtime. Work submitted to a sycl::queue can execute once certain prerequisites tracked by the SYCL runtime are met, such as availability of input data. These prerequisites are described in more detail in Chapters 3 and 8.

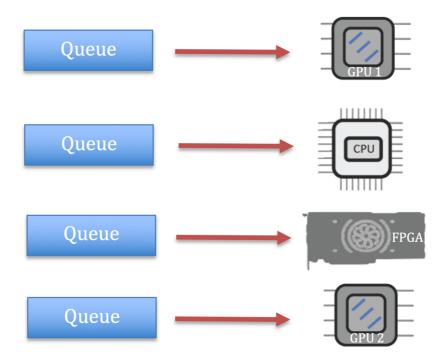

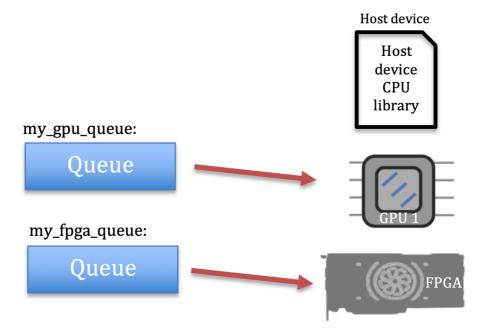

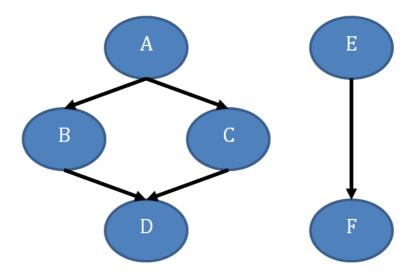

A sycl:: queue is bound to a single sycl:: device, and that binding occurs on construction of the queue. It is important to understand that work submitted to a queue is executed on the single device to which that queue is bound. Queues do not map to collections of devices, for example, where there would be ambiguity on which device would perform the enqueued work. Similarly, a queue cannot spread the work submitted to it across multiple devices. Instead, there is an unambiguous and one-to-one mapping between a queue, and the device on which work submitted to that queue will execute, as shown in Figure 2-3.

Figure 2-3: Queues are bound one-to-one to a specific device. Work submitted to the queue executes on that device. SYCL developers construct queues in their host code, so choose how many are needed for an application.

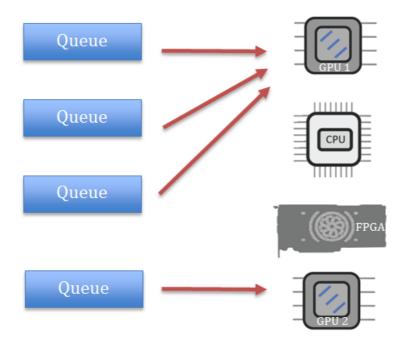

Multiple queues may be created in a SYCL application, as desired for application architecture or programming style. For example, multiple queues may be created to each bind with a different device, or to be used by different threads in a host program. Any number of queues can be bound to a single device, such as a GPU, and submissions to different queues bound to the same device will result in the combined work being performed on that single device. An example of such a binding is shown in Figure 2-4. Conversely, a queue cannot be bound to more than one device. Queues bind only to a single device so that there is no ambiguity on where work submitted to a queue will execute. If a user wants a queue that will load balance work across multiple devices, for example, then they can create that abstraction in their code.

Figure 2-4: Multiple queues can be bound to a single device, and the combination of work submitted to such queues is combined onto the device. The converse is not allowed, though, and a single queue cannot be bound to more than one device, because it would lead to ambiguity in where device code will execute.

Because a queue is bound one-to-one with a device, queue construction is the most common location in SYCL code to choose the device on which the queue submissions will execute. Selection of the device is achieved through a device selector abstraction and associated sycl::device\_selector class.

## Binding a queue to a device, when any device will do

```

#include <CL/sycl.hpp>

#include <iostream>

using namespace cl::sycl;

int main() {

// Create queue on whatever default device SYCL

// implementation chooses. Implicit use of the default_selector().

queue myQueue;

std::cout << "Selected device: " <<

myQueue.get_device().get_info<info::device::name>() << "\n";

return 0;

}

Possible output:

Selected device: SYCL host device</pre>

```

Figure 2-5 provides an example code listing, where the device with which a queue will be bound is not specified. The trivial queue constructor, that doesn't take any arguments (as in Figure 2-5), simply chooses some available device behind the scenes. SYCL guarantees that at least some device will be available, which might be the SYCL host device that is a device abstraction of the processor(s) on which the host code is executing.

```

#include <CL/sycl.hpp>

#include <iostream>

using namespace cl::sycl;

int main() {

// Create queue on whatever default device SYCL

// implementation chooses. Implicit use of the default_selector().

queue myQueue;

std::cout << "Selected device: " <<

myQueue.get_device().get_info<info::device::name>() << "\n";

return 0;

}

Possible output:

Selected device: SYCL host device</pre>

```

Figure 2-5: Implicit default device selector through default construction of a queue.

Using the default queue constructor is a simple way to start application development, and to get device code running quickly. Additional control over selection of

the device bound to a queue can be added as it becomes relevant for application development.

# Method#2: Using the host device for development and debugging

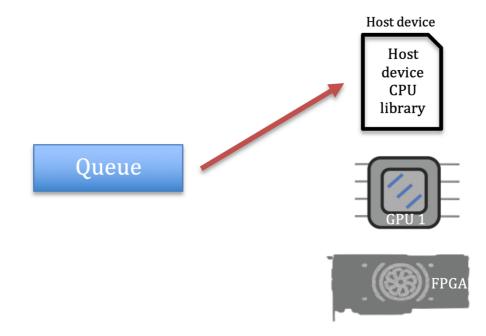

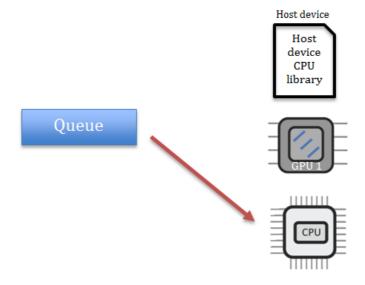

The host device can be thought of as enabling the host CPU to act as if it was an independent device, allowing device code (with the associated built-ins) to be executed regardless of the accelerators available in a system. It also has the fundamental property that it is always available to a SYCL application. The host device therefore provides a guarantee that device code can always be run within an application (no dependency on accelerator hardware), and has three primary uses:

- 1. **Development of device code** on less capable systems that don't have any accelerators. One common use is development and testing of SYCL device code on a local system, before deploying to an HPC cluster for performance testing and optimization.

- 2. **Debugging of device code** with non-accelerator tooling. Accelerators are often exposed through lower level APIs that may not have debug tooling as advanced as is available for host CPUs. With this in mind, the host device is expected to support debugging using standard tools familiar to CPU developers.

- 3. **Backup** if no other devices are available, to guarantee that device code can be executed functionally. The host device implementation may not have performance as a primary goal, so should be considered as a functional backup to ensure that device code can always execute in any SYCL application, but not necessarily a path to performance.

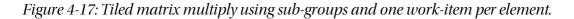

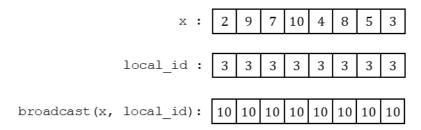

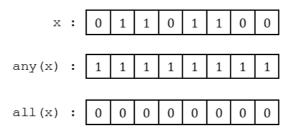

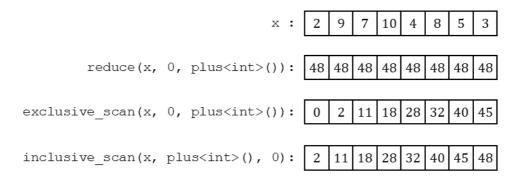

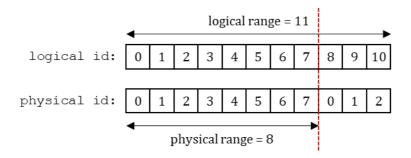

The host device is functionally like a hardware accelerator device in that a queue can bind to it, and it can execute device code. Figure 2-6 shows how the host device is a peer to other accelerators that might be available in a system. It can execute device code, just like a CPU, GPU or FPGA, and can have one or more queues constructed that bind to it.